Fakhreddine Ghaffari's HomePage

Fakhreddine Ghaffari,

ETIS, UMR 8051,

6, avenue du Ponceau,

F-95000, Cergy-Pontoise,

France

Tel: (+33) 1 30 73 66 13

Mobile:(+33) 6 13 97 31 85

Fax: (+33) 1 30 73 66 27

fakhreddine.ghaffari@ensea.fr

Subject of research

Keywords:

FPGA Reliability, Design of hardware LDPC decoder/encoder, Transient faults, Models of faults, faults injection/detection/correction/tolerance, critical bits, hostile environment, Reliability of On-chip memory, BRAM, SRAM-based FPGA, ASIC, EEG for BCI, Real Time Operating System, Critical systems, embedded systems, Real time systems, Dedicated architecture, Design of system-on-chip.

Description:

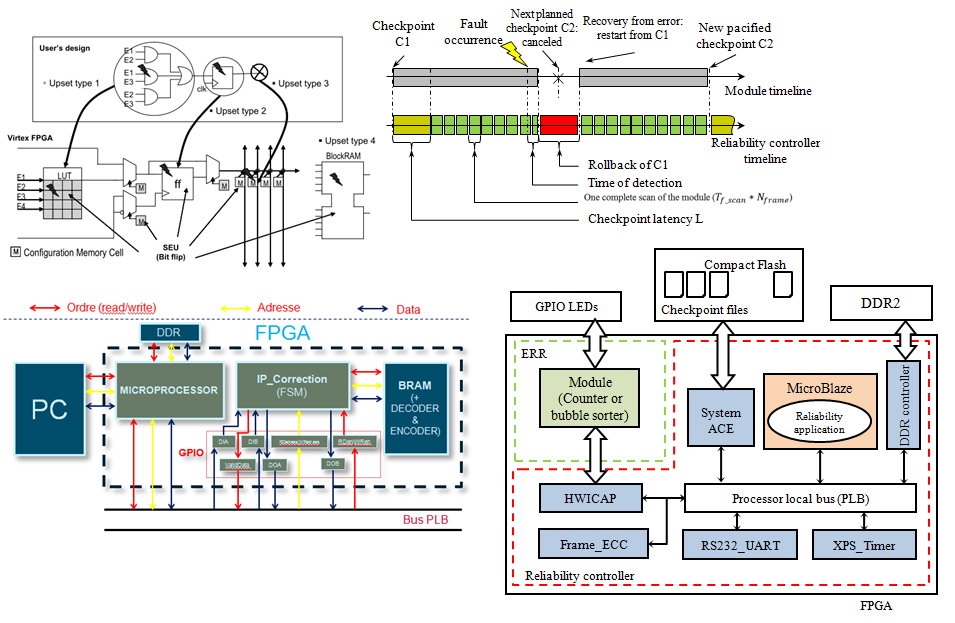

With components on the chips becoming smaller and the number of such components increasing exponentially, even if reliability of the components remains same, total reliability of the chip goes down. More number of components increases the probability of failure on a chip, principally in 28nm technology and below. We offer solutions for transient faults tolerance to design a reliable SoCs especially a dynamically reconfigurable systems. We develop tailored and multi-level approaches of reliability passing through the modeling of faults, the injection companion (by simulation, emulation, critical bits), the detection of single and multiple faults, confinement / isolation, mapping circuit , correction and / or fault tolerance (Checkpoint / Recovery, redundancy, ECC algorithms, partial reconfiguration, Backward / Forward Error recovery). We validate our reliability mechanisms by deployment of industrial application (Aerospace, Automotive …) on reconfigurable platforms (Xilinx Spartan, Virtex 5/6/7/Zynq, Altera Cyclone / Sratix V ...)

Figures:

Demonstration: